- [38] A. van der Ziel, "Thermal noise in field-effect transistors," *Proc. IRE*, vol. 50, pp. 1808-1812, 1962.

- [39] W. Baechtold, "Noise behavior of GaAs field-effect transistors with short gate lengths," *IEEE Trans. Electron Devices*, vol. ED-19, pp. 674-680, May 1972.

- [40] NE244 Data Sheet, California Eastern Labs, Santa Clara, CA.

- [41] K. Takagi and A. van der Ziel, "High frequency excess noise and flicker noise in GaAs FET's," *Solid-State Electron.*, vol. 22, pp. 285-287, 1979.

- [42] J. Graffeuil, "Static, dynamic, and noise properties of GaAs Mesfets," Ph.D. thesis, Univ. Paul Sabatier, Toulouse, France.

- [43] H. Rothe and W. Dahlke, "Theory of noisy fourpoles," *Proc. IRE*, vol. 44, no. 6, pp. 811-818, June 1956.

- [44] H. Fukui, "Design of microwave GaAs MESFET's for broad-band low-noise amplifiers," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-27, no. 7, pp. 643-650, July 1979.

- [45] Type D-5880 RT/Duroid, .031" dielectric, 1 oz. 2 side copper, Rogers Corp., Chandler, AZ.

- [46] S. Weinreb, M. Balister, S. Maas, and P. J. Napier, "Multiband low-noise receivers for a very large array," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-25, no. 4, pp. 243-248, Apr. 1977.

- [47] Indalloy No. 4 Solder, 100% Indium, 157°C, Indium Corp. of America, Utica, NY.

- [48] #30 Supersafe Flux (water soluble), Superior Flux and Mfg. Co., Cleveland, OH.

- [49] SN62 Solder, 62% Tin, 36% Lead, 2% Silver, 179°C, Multicore Solder, Westbury, NY.

- [50] 20E2 Solder, 100°C, Alpha Metals, Jersey City, NJ.

- [51] #74 Polyester Electrical Tape, 3M Co., Minneapolis, MN.

- [52] L. Nevin and R. Wong, "L-band GaAs FET amplifier," *Microwave J.*, vol. 22, no. 4, p. 82, Apr. 1979.

- [53] J. Frey, "Effects of intervalley scattering on noise in GaAs and InP field effect transistors," *IEEE Trans. Electron Devices*, vol. ED-23, no. 12, pp. 1298-1303, Dec. 1976.

- [54] J. Granlund, "Resistance associated with FET gate metallization," *IEEE Trans. Electron Devices*, to be published.

- [55] N. J. Keen, "The role of the undepleted epitaxial layer in low noise Schottky barrier diodes for millimeter wave mixers," Max-Planck-Institute for Radio Astronomy, Bonn, W. Germany, to be published.

- [56] S. Sesnic and G. Craig, "Thermal effects in JFET and MOSFET devices at cryogenic temperatures," *IEEE Trans. Electron Devices*, vol. ED-19, no. 8, pp. 933-942, Aug. 1972.

- [57] D. Brunet-Brunol, "Etude et réalisation d'amplificateur a transistor a effet de champ a l'GaAs refroidi a très basse température," *Rev. Phys. Appl.*, vol. 13, no. 4, pp. 180-187, Apr. 1978.

- [58] S. Weinreb and T. M. Brookes, "Characteristics of low-noise GaAs MESFET's from 300 K to 20 K," in *Proc. European Microwave Conf.*, 1980.

- [59] COMPACT Network Analysis Program, Compact Engineering Inc., Palo Alto, CA.

# Design of Broad-Band GaAs FET Power Amplifiers

CHRISTEN RAUSCHER, MEMBER, IEEE, AND HARRY A. WILLING, MEMBER, IEEE

**Abstract**—A direct systematic approach to designing broad-band GaAs FET power amplifiers for optimum large-signal gain performance is described. Assets of this approach include its accuracy in predicting large-signal amplifier performance and its basic simplicity. The implementation of the technique is facilitated by having to measure large-signal device behavior at only one single frequency. The practicability of the method is demonstrated through comparisons between measured and predicted results.

## I. INTRODUCTION

MICROWAVE GaAs FET's are being used extensively in a wide variety of circuit applications. One of their prominent uses is in large-signal quasi-class-A amplifiers. This paper describes a systematic design procedure for optimizing broad-band gain performance in such amplifiers [1]. Principal assets of the approach are its accuracy in predicting amplifier response at elevated gain compression levels and its simplicity. The simplicity of the method is attributed to the use of a special circuit-type

model to describe large-signal device performance. The principal function of the model is to cast device performance characteristics into an easily manageable format which ultimately permits the nonlinear circuit design problem to be solved efficiently with existing linear synthesis techniques. The derivation of the model proves to be remarkably simple by itself, based solely on large-signal device information obtained experimentally at a single reference frequency. Important to the practical significance of the method is, of course, that its underlying simplicity not stand in the way of accurately predicting large-signal amplifier performance. This is accomplished by focusing on the device nonlinearities that control power gain behavior, and by limiting design considerations to amplifier performance at a designated fixed output power level specified by the particular application.

## II. THE METHOD

### A. Basic Design Philosophy

The design objective is to achieve maximum flat gain across the frequency band of interest with the transistor

Manuscript received April 30, 1980; revised June 26, 1980.

The authors are with Naval Research Laboratory, Code 6851, Washington, DC 20375.

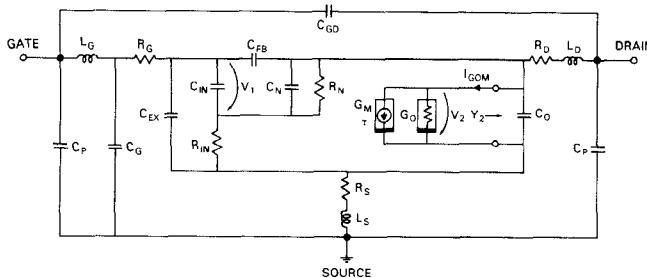

Fig. 1. Circuit-type model of a GaAs MESFET.

operating at a prescribed nominal RF output power level  $P_{\text{NOM}}$ . Focus, thereby, is primarily on *fundamental-frequency* effects. The basic strategy adopted in the present approach is to aim for broad-band conjugate match at the transistor output, while essentially relying on the input matching circuit to neutralize the intrinsic gain slope of the device.

Establishing conjugate matching conditions at the output intuitively appears to be the obvious choice, knowing that nonlinear device-circuit interaction in amplifiers is predominantly associated with the drain-source port of the device [2]–[5]. This choice does, indeed, constitute a viable assumption in the present context by providing the basis for the conceptual simplicity of the technique to be described without compromising the design objective. For the sake of completeness it should be noted, nevertheless, that a certain degree of design flexibility exists at the lower passband frequencies where excess gain is available. By introducing appropriate mismatch at the output, this flexibility can theoretically be used to improve gain bandwidth performance, or to improve linearity at the low end of the band over that achievable at the high end. The technique can be readily generalized to encompass these possibilities. This option, however, has generally relatively limited practical value and is hence not given further consideration here.

The key to simplicity and numerical efficiency of the design procedure is the use of a large-signal model representation of the device which is compatible with standard frequency-domain synthesis techniques. The derivation of the model and its underlying justification are discussed in the following.

### B. Large-Signal Device Model

The topology assigned to the circuit-type device model is shown in Fig. 1 and is similar to the basic configuration associated with the quasi-static nonlinear model reported earlier [4], [5]. Unlike the generalized cases addressed in those investigations, only the transconductance  $G_M$  and the output conductance  $G_O$  need to be considered nonlinear elements in the present context. The validity of this working assumption has been confirmed earlier through numerical sensitivity analyses of large-signal effects in quasi-class-A amplifiers in which  $G_M$  and  $G_O$  have been identified as being predominantly responsible for these effects.

According to [5], the combined currents through cur-

rent generator and output conductance can be expressed in the form

$$i_{\text{GOM}}(t) = i_{\text{GOM}}(v_1(t-\tau), v_2(t)) \quad (1)$$

with the parameters defined in Fig. 1, and the time delay  $\tau$  included for generality. The relationship is constrained by the requirement to approximate conjugate output matching conditions within the passband  $[\omega_A, \omega_B]$ , thus (Fig. 1)

$$\text{Im}\{Y_2(\omega)\} = \text{Im}\left\{-\frac{i_{\text{GOM}}(\omega)}{V_2(\omega)}\right\} \approx 0, \quad \omega_A \ll \omega \ll \omega_B. \quad (2)$$

Relation (2) can be interpreted as defining a frequency-dependent load-line in the dynamic  $I$ - $V$  characteristics [5] associated with the time-invariant expression (1). Due to the load-line constraint, the voltage variables  $V_1(\omega)$  and  $V_2(\omega)$  become interrelated. This allows the device nonlinearities to be expressed, for instance, solely in terms of the variable  $V_2(\omega)$ .

From a practical point of view, it would be more convenient to work with a quantity that can be readily measured, such as the RF power  $P_{\text{OUT}}$  delivered to a matched load, rather than with the intrinsic voltage  $V_2(\omega)$ . The two variables  $V_2$  and  $P_{\text{OUT}}$  are, however, closely linked to each other. Assuming perturbations in  $P_{\text{OUT}}(\omega)$  due to parasitic feedback and losses in source and drain lead resistances to be small relative to  $P_{\text{OUT}}(\omega)$ , and with  $P_{\text{OUT}}(\omega)$  required to be in the vicinity of its specified nominal value  $P_{\text{NOM}}$ , the approximate relationship

$$|V_2(\omega)| = \alpha(\omega) \cdot \sqrt{P_{\text{OUT}}(\omega)} \approx \alpha(\omega) \cdot \sqrt{P_{\text{NOM}}} \quad (3)$$

may be used. For a broad-band conjugate match at the output, the proportionality factor  $\alpha(\omega)$  can be regarded as essentially constant, thus permitting the device nonlinearities to be expressed in terms of  $P_{\text{NOM}}$  with the current  $i_{\text{GOM}}$  written as

$$i_{\text{GOM}}(\omega) = V_1(\omega) e^{j\omega\tau} \cdot \bar{G}_M(P_{\text{NOM}}) + V_2(\omega) \cdot \bar{G}_O(P_{\text{NOM}}). \quad (4)$$

Symbols  $\bar{G}_M$  and  $\bar{G}_O$  stand for the effective large-signal values of transconductance and output conductance, respectively. It is important to note that these values are defined as frequency-independent quantities and are only functions of the design-invariant  $P_{\text{NOM}}$ .

With introduction of relationship (4), the initial nonlinear synthesis problem is reduced to a linear design task to which conventional frequency-domain techniques can be applied. Crucial to the viability of this approach is that the linearized relation (4) is not only valid for conjugate output matching conditions, but also provides a good working approximation for near-conjugate conditions as occur in practical amplifiers. This follows from the fact that the incremental sensitivity of  $P_{\text{OUT}}$  with respect to changes in load impedance vanishes by definition for a conjugately matched output.

Determination of the complete large-signal model, and the values of  $\bar{G}_M(P_{\text{NOM}})$  and  $\bar{G}_O(P_{\text{NOM}})$  in particular,

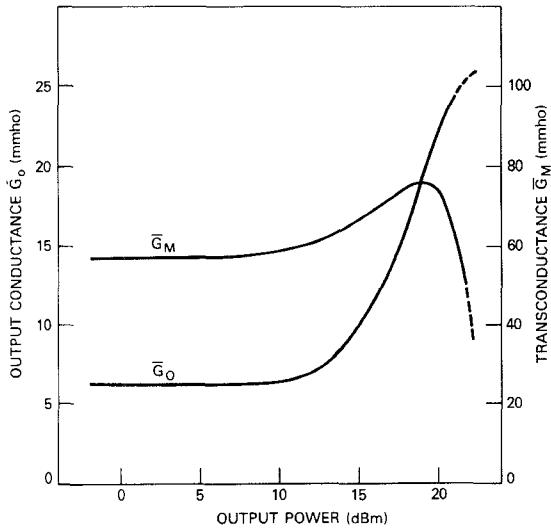

Fig. 2. Effective large-signal transconductance  $\bar{G}_M$  and output conductance  $\bar{G}_O$  for a single cell of an Avantek low-noise M110 device. (Gate length:  $0.5 \mu\text{m}$ ; gate width:  $375 \mu\text{m}$ ;  $I_{DSS}$  at  $V_{DS} = +3 \text{ V}$ :  $105 \text{ mA}$ ; bias voltages:  $V_{GS} = -1 \text{ V}$  and  $V_{DS} = +3 \text{ V}$ ).

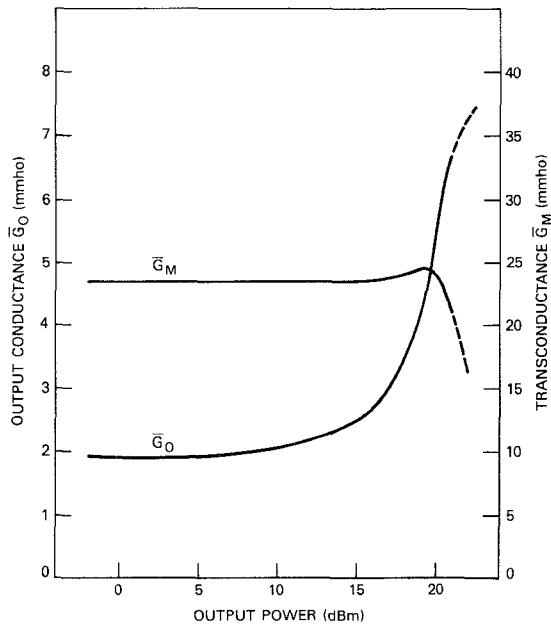

Fig. 3. Effective large-signal transconductance  $\bar{G}_M$  and output conductance  $\bar{G}_O$  for a Texas Instruments medium power device. (Gate length:  $1.0 \mu\text{m}$ ; gate width:  $300 \mu\text{m}$ ;  $I_{DSS}$  at  $V_{DS} = +6 \text{ V}$ :  $80 \text{ mA}$ ; bias voltages:  $V_{GS} = -2 \text{ V}$  and  $V_{DS} = +6 \text{ V}$ ).

starts out by finding the small-signal values of the elements in the topology given in Fig. 1. This is accomplished by fitting the model, in the standard fashion, to small-signal device  $S$ -parameters measured with respect to the bias point to be employed in the final amplifier. The small-signal values of  $\bar{G}_M$  and  $\bar{G}_O$  are subsequently reoptimized in order for the modified linear model to accurately represent the *large-signal* gain performance of the device for optimally matched conditions at the output over the entire frequency band of interest. The refitting process calls for little additional numerical effort, as it merely involves a circuit optimization with *two* real variables. It is

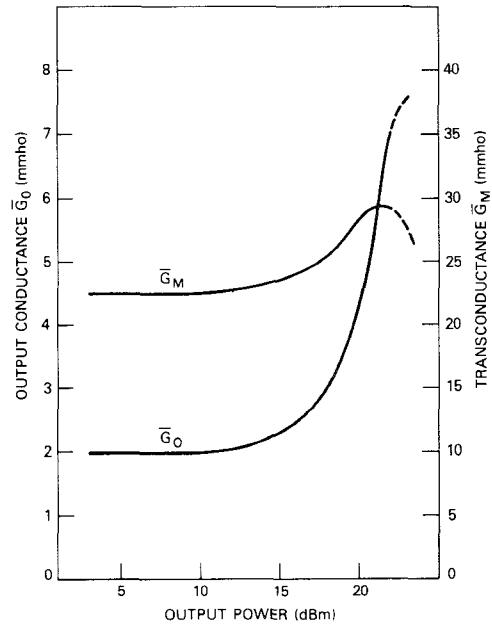

Fig. 4. Effective large-signal transconductance  $\bar{G}_M$  and output conductance  $\bar{G}_O$  for a Texas Instruments power device. (Gate length:  $1.7 \mu\text{m}$ ; gate width:  $600 \mu\text{m}$ ;  $I_{DSS}$  at  $V_{DS} = +6 \text{ V}$ :  $140 \text{ mA}$ ; bias voltages:  $V_{GS} = -2 \text{ V}$  and  $V_{DS} = +6 \text{ V}$ ).

important to note that—due to the frequency-independence of  $\bar{G}_M(P_{\text{NOM}})$  and  $\bar{G}_O(P_{\text{NOM}})$ —the reoptimization of the model need involve only a single reference frequency. This frequency may be selected arbitrarily, in principle, but for practical considerations is normally chosen to lie within the band of interest. The large-signal information utilized in the reoptimization process consists of the load impedance value for conjugate match and the associated gain measured at the selected frequency, with the device operating at the designated nominal output power level  $P_{\text{NOM}}$ . The simple measurement task can be performed, for instance, with an experimental setup similar to the one described in [5].

### C. Experimental Verification of the Model

Parameters for the linearized large-signal model have been determined as described for three individual devices of appreciably differing physical and electrical characteristics. The devices subjected to detailed investigation are a) one cell of an Avantek low-noise M110 device with a  $0.5\text{-}\mu\text{m} \times 375\text{-}\mu\text{m}$  gate geometry, b) a Texas Instruments medium power transistor with a  $1.0\text{-}\mu\text{m} \times 300\text{-}\mu\text{m}$  gate geometry, and c) a  $600\text{-}\mu\text{m}$  power device, also from Texas Instruments, with a gate length of  $1.7\text{-}\mu\text{m}$ . The effective large-signal values of  $\bar{G}_M$  and  $\bar{G}_O$  have been evaluated for these devices as functions of power delivered to a matched load. For the purpose of illustration, these values have been determined for a wide range of output power levels  $P_{\text{OUT}}$  as depicted in Figs. 2–4. (It should be emphasized, however, that when designing an amplifier for a specified nominal output power level  $P_{\text{NOM}}$  only *one* particular point on each of the curves is required.) Except for operation at very high gain compression, the values of  $\bar{G}_O$

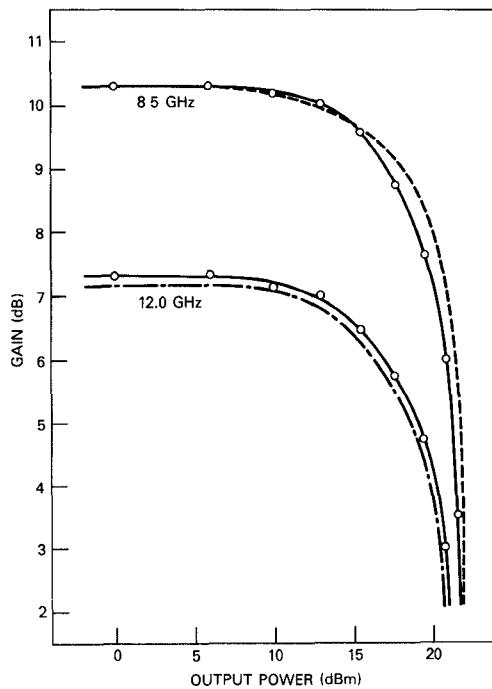

Fig. 5. Gain versus output power at 8.5 and 12.0 GHz for one cell of the Avantek M110 device, input port untuned. -○- - - Measured response. - - - Predicted response, coincides with measured response at 8.5 GHz. - - - Exponential approximation to 8.5-GHz response.

prove to be considerably more sensitive to drive level than the corresponding values of  $\bar{G}_M$ . Gain saturation effects for the chosen bias conditions are thus seen to be associated primarily with nonlinear behavior of the output conductance.

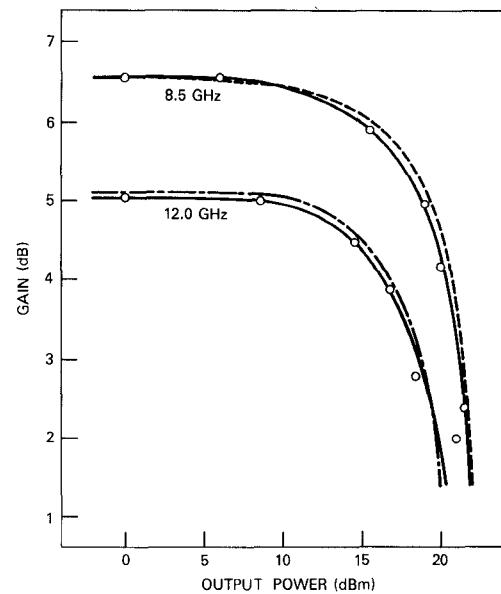

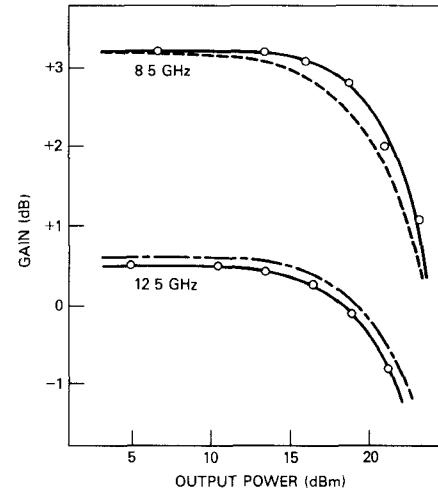

Figs. 5–7 serve to demonstrate the ability of the model to predict large-signal gain performance at frequencies remote from the reference frequency used in the modeling process. This ability distinguishes the current technique from linearization schemes, such as the one employed in [6], which basically applies to only one frequency at a time. The inherent broad-band aspect of the present approach is illustrated by comparing model-predicted large-signal gain behavior to measured device data. The input of the device was deliberately left untuned ( $50\Omega$  system) for this comparison in order to simplify the acquisition of reliable measurement results without affecting the relevance of the comparison. The uppermost solid-line curves in Figs. 5–7 represent the gain responses of the three test devices versus output power delivered to matched loads at the chosen reference frequency of 8.5 GHz. Measured and predicted points coincide by virtue of the modeling process carried out for a representative number of discrete power levels at that frequency. (The approximations to the 8.5-GHz responses indicated with broken lines are discussed in Section II-D.) Without further modifying the parameters of the individual models, they were subsequently used to predict large-signal gain at the upper end of X-band. The two lower curves in Figs. 5–7 demonstrate close agreement between these predictions and corresponding experimental data.

Fig. 6. Gain versus output power at 8.5 and 12.5 GHz for the Texas Instruments 1.0- $\mu$ m device, input port untuned. -○- - - Measured response. - - - Predicted response, coincides with measured response at 8.5 GHz. - - - Exponential approximation to 8.5-GHz response.

Fig. 7. Gain versus output power at 8.5 and 12.0 GHz for the Texas Instruments 1.7- $\mu$ m device, input port untuned. -○- - - Measured response. - - - Predicted response, coincides with measured response at 8.5 GHz. - - - Exponential approximation to 8.5-GHz response.

The reliability and consistency of the predictions serve to further confirm the validity of the basic assumption that device nonlinear performance in amplifiers can be accurately modeled with nonlinearity confined to transconductance and output conductance. It is believed that this observation represents a characteristic typical of GaAs FET's in general, as it equally applied to all three devices investigated, originating from two different manufacturers and spanning the range of gate lengths from 0.5 to 1.7  $\mu$ m. In defining the nonlinear model element values as functions of RF power, special care has been taken to assure the accuracy of the performed load pull measurements as well as to realistically assess device parasitics. It is cau-

tioned that without such assurance erroneous conclusions are likely to result, leading to an apparent necessity to generalize the model by introducing additional nonlinear elements, such as a nonlinear output capacitance.

The dependence of device input reflection coefficient on drive level was also investigated. It was found that the model with its two nonlinear elements at the output provides correct predictions of this dependence. Variations in input reflection coefficient, which are generally relatively small, are due to feedback effects and are directly linked to the variation of transconductance and output conductance with drive level.

#### D. Choice of Nominal Output Power Level

The large-signal model is derived on the assumption that amplifier performance is to be optimized relative to a specified nominal output power level  $P_{\text{NOM}}$ . This value is generally determined by large-signal gain requirements, such as limits imposed on gain compression. Tradeoff considerations are easily dealt with on the basis of measured output power delivered to a conjugately matched load versus input power at the highest passband frequency  $\omega_B$ , with Figs. 5–7 serving as examples.

An alternate approach is to bypass most of the experimental effort by relying on an empirical relationship [7] for estimating gain  $\Gamma$  as a function of drive level  $P_{\text{IN}}$ :

$$\Gamma(P_{\text{IN}}) \approx \frac{P_{\text{MAX}}}{P_{\text{IN}}} \cdot \left\{ 1 - \exp\left(-\frac{P_{\text{IN}}}{P_{\text{MAX}}} \cdot \Gamma_{P_{\text{IN}} \rightarrow 0}\right) \right\} \Big|_{\omega=\omega_B} \quad (5)$$

where  $P_{\text{MAX}}$  denotes the maximum available saturated output power. Unlike other empirical expressions investigated in the present context, relationship (5) provides an astonishingly good fit to measured data as indicated by the broken lines in Figs. 5–7. It has also been found that for obtaining a rough initial estimate of device gain compression characteristics, the value of  $P_{\text{MAX}}$  in (5) may be approximated

$$P_{\text{MAX}} \approx \frac{2}{\pi^2} \cdot \frac{1}{R_{LL}} \cdot V_{DS\text{max}}^2 \quad (6)$$

where  $R_{LL}$  is the resistance of the load line that yields maximum current-times-voltage swing in the  $I_{DS}$ – $V_{DS}$  plane, and  $V_{DS\text{max}}$  is the associated maximum peak-to-peak (square-wave) voltage swing.

### III. AMPLIFIER EXAMPLE

As outlined in the previous section, the large-signal model forms the foundation of the present approach. Once the model has been defined, the design of the amplifier, employing classical linear synthesis techniques, is straightforward. To further illustrate the usefulness of the method, it has been applied to the design of an 8- to 12-GHz power amplifier. The 1.0- $\mu\text{m}$  device from Texas Instruments referred to earlier has been used in this amplifier. The design was intended to provide power gain in excess of 5 dB across the band at an incident power level of +15 dBm. The input and output matching networks are composed of five and four distributed micro-

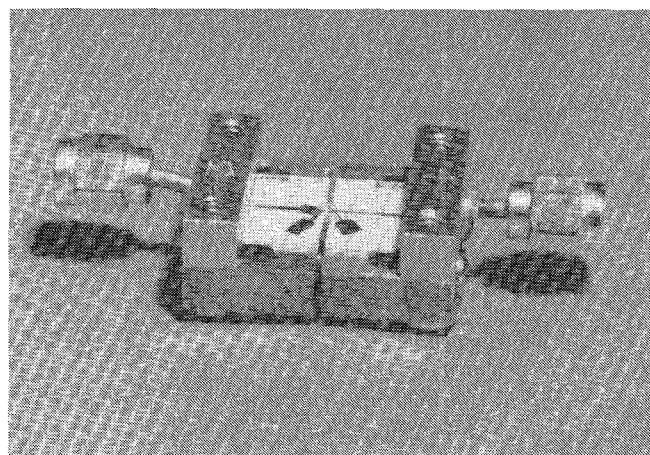

Fig. 8. Example of an 8- to 12-GHz GaAs FET amplifier designed for optimum large-signal gain performance.

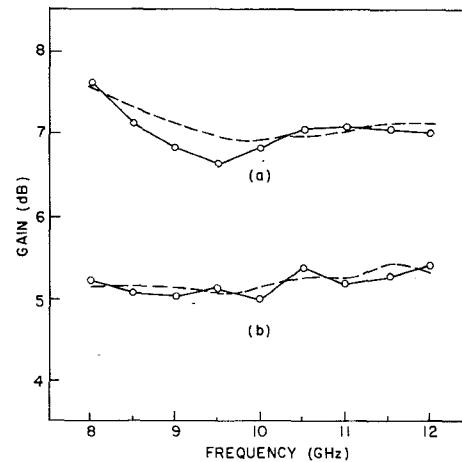

Fig. 9. Gain performance of the 8- to 12-GHz GaAs FET power amplifier (a) Small signal. (b) Incident power level of +15 dBm. — Measured ---- Predicted.

strip elements, respectively. The implementation on a 0.635-mm (25-mil) thick alumina substrate is shown in Fig. 8. In order to avoid potential sources of uncertainty in interpreting experimental results, external bias circuits were used.

The comparison between measured (untweaked) and predicted gain performance of this amplifier is given in Fig. 9 for both small-signal and large-signal operation. Although they are no real concern, the minor discrepancies at the small-signal level were, nevertheless, investigated more closely. It was found that these deviations were largely due to the imperfections associated with the SMA connectors used in the coaxial to microstrip adaptors. It is interesting to note that similar deviations are not observed at the higher drive level. This is attributed to the point stated earlier, namely that the performance of the optimum large-signal design is insensitive to perturbations of the terminating impedance values.

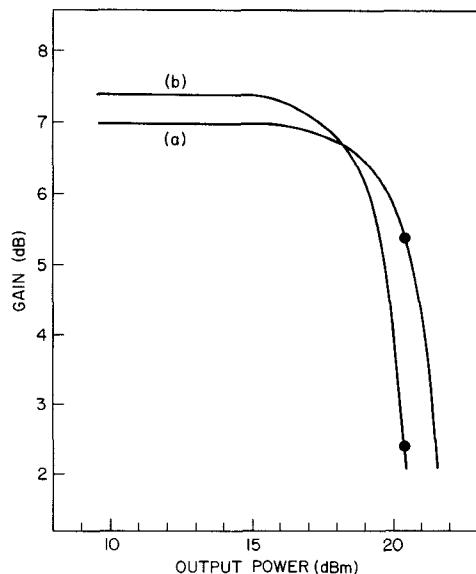

Curve (a) in Fig. 10 shows the measured saturation characteristics of the amplifier at 12 GHz. The dot on the curve indicates the nominal large-signal operating point for which the amplifier was designed. Curve (b) represents the measured characteristics of the same amplifier with its

Fig. 10. Gain compression as a function of output power measured at 12 GHz. (a) Response of the 8- to 12-GHz amplifier optimized for large-signal performance. (b) Response of the same amplifier, but with its output circuit retuned externally for maximum *small-signal* gain.

output port retuned for maximum *small-signal* gain. The retuning of the output was simulated with the aid of an external tuning arrangement [5]. This experiment quantitatively illustrates the reduction in large-signal gain which would result if achieving the nominal output power level had been attempted with only a small-signal design.

#### IV. CONCLUSIONS

A systematic procedure has been described for designing GaAs FET power amplifiers for optimum large-signal gain performance. The technique has been applied, specifically, to broadband quasi-class-A circuits. The

principal merits of the method include remarkable simplicity and numerical efficiency of the overall design procedure, reliability in predicting large-signal amplifier performance, and the need to acquire experimental large-signal data only at one particular frequency. The viability of this approach has been verified through various comparisons between measured and predicted results for three individual devices exhibiting considerably differing geometries and electrical characteristics.

#### ACKNOWLEDGMENT

The authors wish to thank Dr. H.-Q. Tserng of Texas Instruments, Inc. and Dr. M. Omori of Avantek for kindly providing the devices used in this study, and Dr. B. E. Spielman and R. E. Neidert for their helpful suggestions.

#### REFERENCES

- [1] C. Rauscher and H. A. Willing, "A new approach to designing broadband GaAs FET amplifiers for optimum large-signal gain performance," in *Proc. 9th Eur. Microwave Conf.*, pp. 287-290, 1979.

- [2] F. N. Sechi and R. W. Paglione, "Design of a high-gain FET amplifier operating at 4.4-5.0 GHz," *IEEE J. Solid-State Circuits*, vol. SC-12, pp. 285-290, June 1977.

- [3] J. W. Monroe, J. G. de Koning, W. M. Kelly, and H. Tokuda, "Spot compression points with equal-gain circles," *Microwaves*, vol. 16, pp. 60-77, Oct. 1977.

- [4] H. A. Willing, C. Rauscher, and P. de Santis, "A technique for predicting large-signal performance of a GaAs MESFET," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-26, pp. 1017-1023, Dec. 1978.

- [5] C. Rauscher and H. A. Willing, "Simulation of nonlinear microwave FET performance using a quasi-static model," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-27, pp. 834-840, Oct. 1979.

- [6] K. L. Kotzebue and E. R. Ehlers, "Simple model of large-signal properties of 1 W FET at 5 GHz," *Electron. Lett.*, vol. 15, pp. 237-238, Apr. 1979.

- [7] K. M. Johnson, "Large signal GaAs MESFET oscillator design using large-signal *S*-parameters," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-27, pp. 217-227, Mar. 1979.

## Power Combining Ladder Network with Many Active Devices

KIYOSHI FUKUI, MEMBER, IEEE, AND SHIGEJI NOGI

**Abstract**—This paper presents a theoretical treatment of a line array of van der Pol oscillators mutually coupled by inductances and connected to a load (i.e., a multiple-device ladder oscillator) aiming to investigate its power-combining capability. A mode analysis approach is used, and it is

shown that this system can provide output power just equal to the sum of the available powers from all active devices when it operates at the first mode. In the case where the optimum load is connected at an end of the ladder structure, some stable modes other than the first mode exist, but no stable simultaneous multimodes are found. A method for suppressing undesired modes is discussed. A distributed-line coupled ladder structure is also treated to give a theoretical basis for building a microwave multiple-device ladder oscillator.

Manuscript received January 11, 1980; revised June 12, 1980.

The authors are with the Department of Electronics, Okayama University, Tsushima-Naka 3-1-1, Okayama, Japan 700.